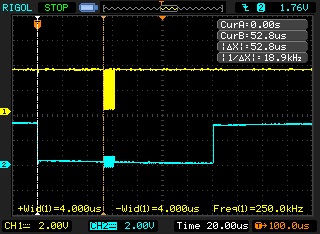

用示波器观察spi的cs和sck,发现cs下降沿到sck第一个下降沿间的时间约有50us,

尝试修改过时钟速率(60M/30M/15M等),CS0或者CS1、ActiveCS RW delay、Deactive CS RW delay都没有直接影响 ,

这个50us的时间间隙对传输速率影响较大,想确定一下是芯片本身就是如何还是说在使用CH347T上位机Demo软件设置的问题?

用示波器观察spi的cs和sck,发现cs下降沿到sck第一个下降沿间的时间约有50us,

尝试修改过时钟速率(60M/30M/15M等),CS0或者CS1、ActiveCS RW delay、Deactive CS RW delay都没有直接影响 ,

这个50us的时间间隙对传输速率影响较大,想确定一下是芯片本身就是如何还是说在使用CH347T上位机Demo软件设置的问题?

您好,如上间隔时间为通过单独的片选函数手动拉片选产生的延迟时间,芯片同时支持硬件SPI自动拉片选的操作。使用硬件SPI控制片选时间精度可控制在5us以内。

假设当前spi时钟为60MHz,以传输512Byte为例,其传输时间约为65us,而这个cs跟sck的间隔都有50us,

即512Byte实际使用了至少 115us,这使得实际有效传输效率降低了几乎一半呀~~~~

对此,该有什么办法可以提高传输效率吗?

1、增大传输包数量?

2、不使用CS?

3、SPI转usb的极限最大传输速率(理想情况下),有测过吗?

谢谢

您好,如上信息已更正,参见#2,使用硬件SPI接口访问可以达到较高的效率,如下所示:

你说的“通过单独的片选函数手动拉片选产生的延迟时间”是指用CH347SPI_SetChipSelect函数吗?

在demo工程里其仅仅在CH347DLL.H有定义,但实际并没有调用过该函数哦。

上述测出的50us是直接用CH347Demo.exe测出的哦,是哪里配置错了吗?

蓝色CS 黄色SCK, 不但前面有约50us时间间隔,后面还有约80us的时间间隔。

蓝色CS 黄色SCK, 不但前面有约50us时间间隔,后面还有约80us的时间间隔。

您好,可以添加我们技术支持微信,协助您看下代码上的使用问题。方式已私信。