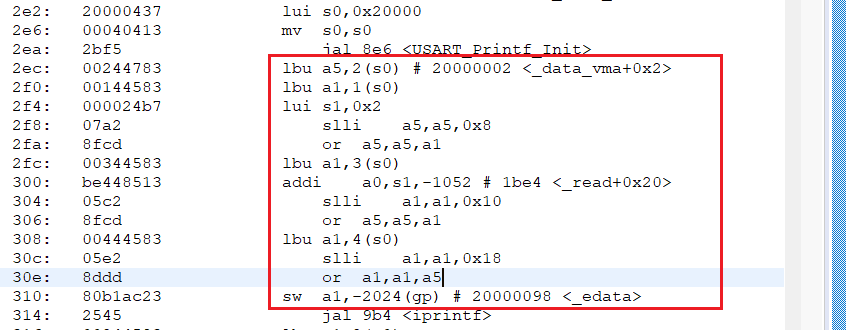

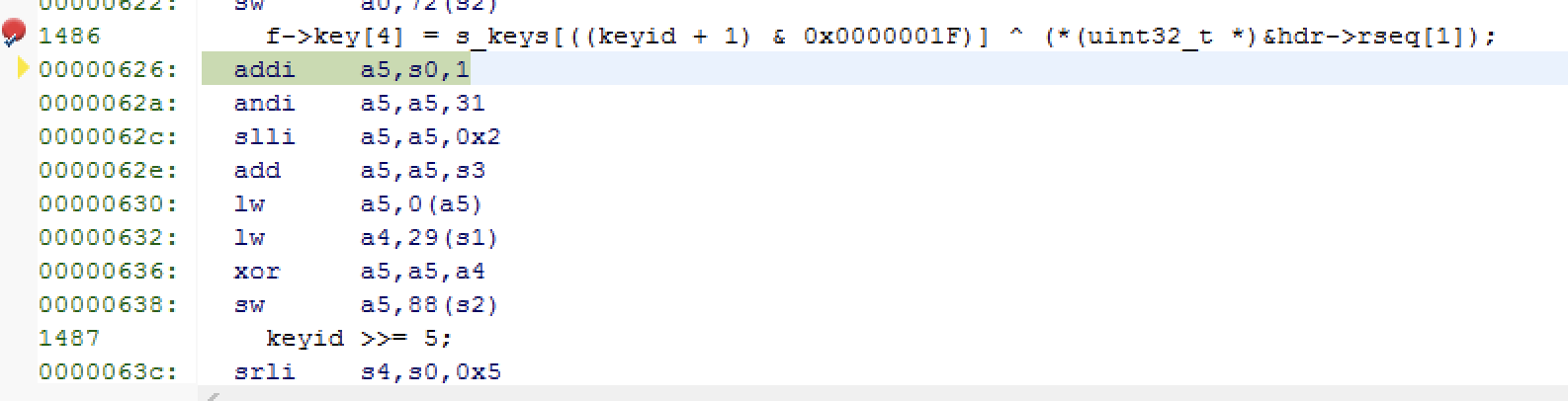

// static const uint32_t s_keys[32]; // uint8_t rseq[16]; f->key[4] = s_keys[((keyid + 1) & 0x0000001F)] ^ (*(uint32_t *)&hdr->rseq[1]);

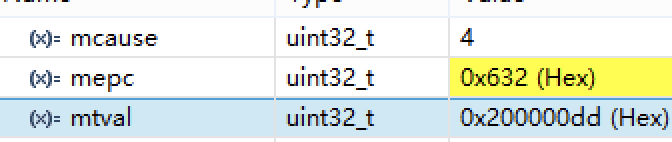

如上面代码,rseq是16字节数据。运行上面代码的时候,直接就是mcause = 4的hardfault,即非对齐load address错误。网上搜了一下,好像说RISC-V还是像CORTEX-M系列那样,能访问,只是速度一样会很慢。但是现在直接hardfault了。不允许非对齐访问不是ARM7年代的问题了?现在移植代码,有不少这些非对齐访问。非常麻烦。是不是编译器参数修改一下就可以非对齐范围?

热门产品 :

CH9120: 网络串口透传芯片