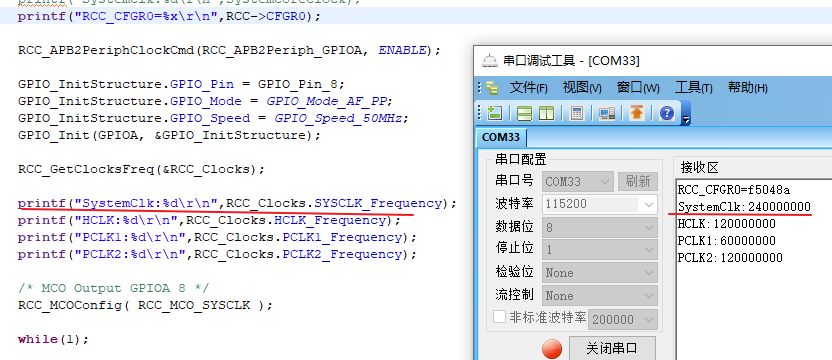

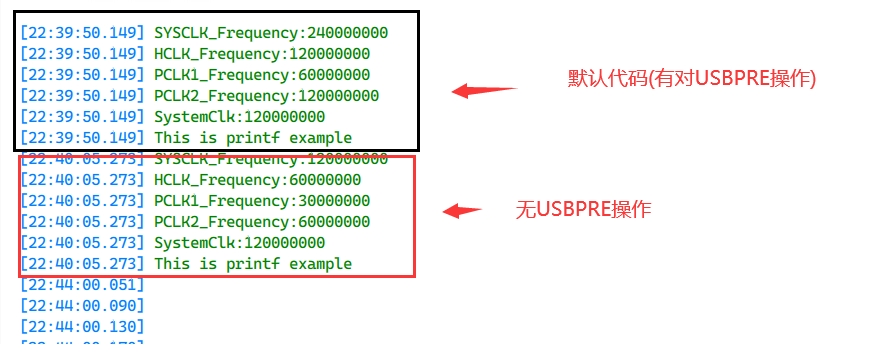

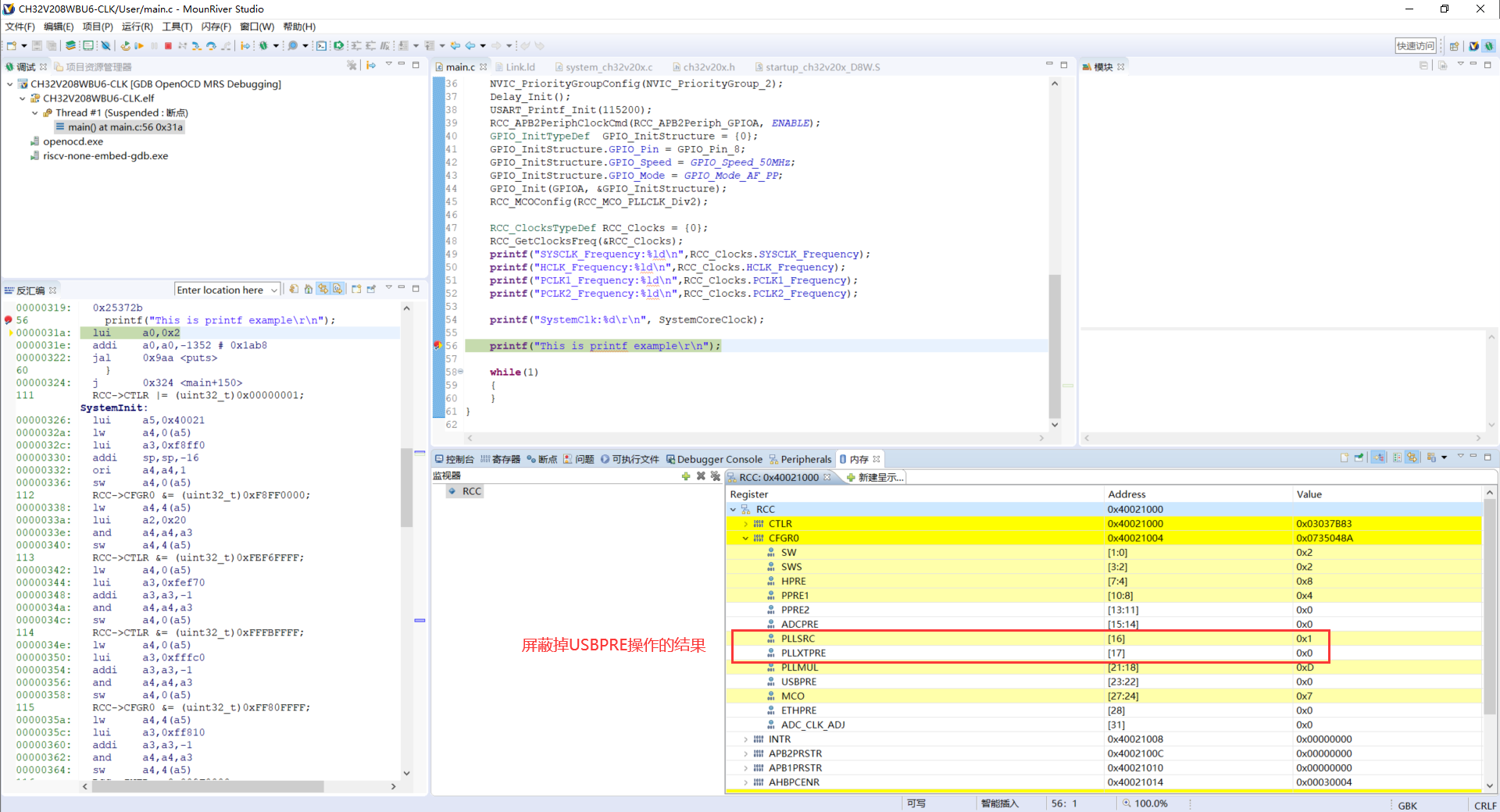

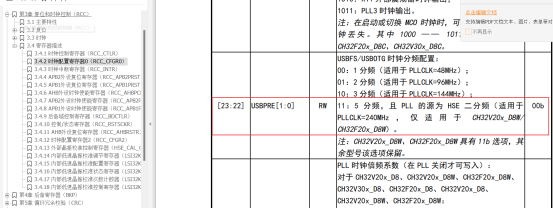

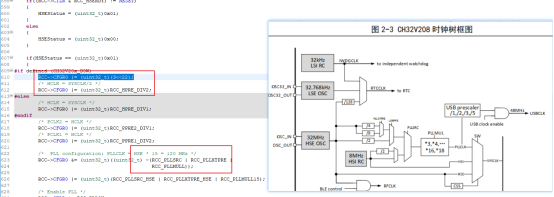

在设置v208时钟的时候发现了一个很奇怪的问题,在官方sdk的SetSysClockTo120_HSE(void)函数中,如果屏蔽掉RCC->CFGR0 |= (uint32_t)(3<<22); rcc-="">CFGR0 |= (uint32_t)(3<<22); 的时候,mco输出是120m,通过查阅手册发现bit[23:22]是设置USBFS/USBOTG 时钟分频的,请问这个分频参数会关系到pll的结果吗?

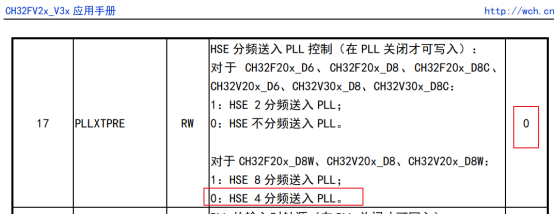

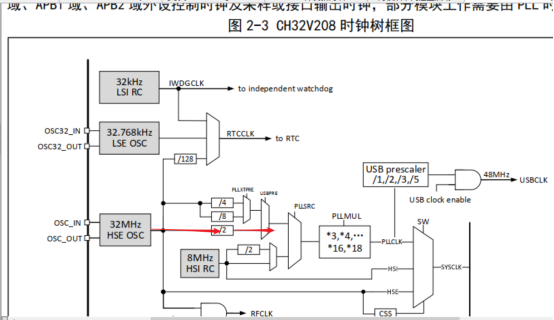

对于这个11 我的理解是:需要先把pll开到240m,即16m*15倍频,然后使用usb的时候需要设置五分频,但是现在的问题是,我已经开到了16m*15倍频,但是不置位11的话,pll的实际时钟只有120m,到不了240m。